VIA TECHNOLOGIES C3 Samuel 2

Description

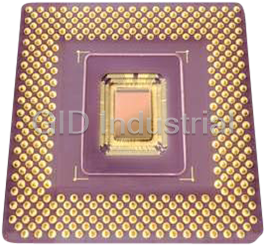

VIA C3 Samuel Processor

Part Number

C3 Samuel 2

Price

Request Quote

Manufacturer

VIA TECHNOLOGIES

Lead Time

Request Quote

Category

Processors

Datasheet

Extracted Text