# DiskOnChip® IDE Pro

#### Flash Disk with IDE Interface

#### **Highlights**

DiskOnChip IDE Pro is a flash disk with an IDE interface. It combines advanced and proven DiskOnChip technology with a standard IDE interface to complement the DiskOnChip product line.

DiskOnChip IDE Pro provides:

- NAND flash-based technology

- High performance

- Platform independence

- Fast time to market no driver required

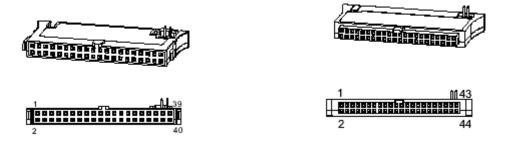

- 40-pin or 44-pin IDE connector

- Hamming code-based EDC/ECC

- 16-bit internal and external operation for 32Mbyte (MB) capacity and higher

- 16-bit external and 8-bit internal operation for 16MB capacity

- IDE Master/Slave modes of operation

#### **IDE Modes**

■ PIO modes 0-4

#### **Performance**

■ Host Data Transfer Rate (Max): 16.6MB/sec

#### **Power Requirements**

- Single power supply: 5V (± 10%)

- Current

- o Active Mode (Max.): 55 mA

- o Sleep/Idle Mode (Max): 0.18 mA

## **Operating Temperature**

■ Temperature Range: 0°C to +70°C

#### **Environmental Conditions**

■ Storage Temperature: -55°C to + 80°C

■ Vibration: 1G, each axis

■ Shock: 10G, 3 axis

#### **System Compatibility**

Compatible with devices that support the ATA-4 Attachment (without DMA support) for Disk Drives Standard.

#### **Capacity and Packaging**

- Available in 16 to 256MB capacity

- Vertical alignment

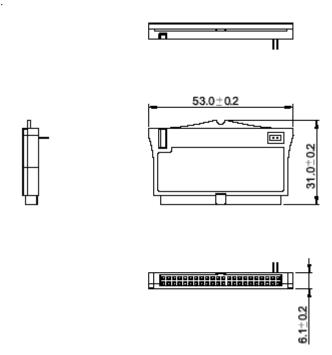

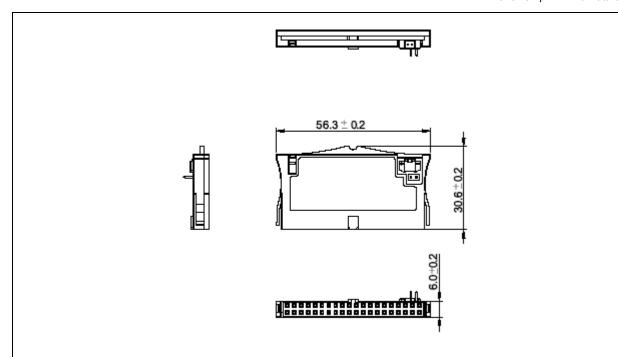

- 40-pin IDE connector (mm): 56.3 x 30.6 x 6.0 (LxWxH)

- 44-pin IDE connector (mm): 53.0 x 31.2 x 6.0 (LxWxH)

#### **Table of Contents** Introduction......4 Product Overview .......5 2.2 Pin Assignment......6 Theory of Operation ......9 Description of Command Block Registers......10 Supported ATA Command Set ......15 5.1.10 5.1.11 5.1.12 5.1.13 5.1.14 5.1.15 5.1.16 5.1.17 5.1.18 5.1.19 5.1.20 5.1.21

|    |      | 5.1.22 Write Sector(s) – 30h, 31h                                         | 32 |

|----|------|---------------------------------------------------------------------------|----|

|    | 5.2  | Valid Error and Status Register Values                                    |    |

| 6. | Inst | allation Requirements                                                     | 35 |

|    | 6.1  | •                                                                         |    |

|    | 6.2  |                                                                           |    |

| 7. | Pov  | ver Management                                                            | 37 |

| 8. | Spe  | ecifications                                                              | 38 |

|    | 8.1  | Environmental Specifications                                              | 38 |

|    | 8.2  | Mechanical Dimensions                                                     | 38 |

|    | 8.3  | Physical Characteristics                                                  |    |

|    | 8.4  | Absolute Maximum Ratings                                                  | 40 |

|    | 8.5  | Electrical Specifications 8.5.1DC Characteristics 8.5.2AC Characteristics | 40 |

| 9. | Ord  | ering Information                                                         |    |

|    |      |                                                                           |    |

#### 1. Introduction

This data sheet includes the following sections:

**Section 1:** Overview of data sheet contents

Section 2: Product overview, including brief product description, pin assignment and description

**Section 3:** Theory of operation

**Section 4:** Descriptions of Command Block registers

**Section 5:** Modes of operation and supported ATA command set

**Section 6:** Installation requirements

**Section 7:** Power Management

Section 8: Environmental, mechanical, electrical and production specifications

**Section 9:** Product ordering information

For additional information on M-Systems' flash disk products, please contact one of the offices listed on the back page.

#### 2. Product Overview

#### 2.1 Product Description

DiskOnChip IDE Pro complements the DiskOnChip product line, offering full IDE capabilities, high performance, a built-in ECC system and flexible design options. It can be used in any system with an IDE bus and can work with any operating system, since the driver is handled at the BIOS level. DiskOnChip IDE Pro offers both internal and external 16-bit operation. This provides for superior performance over other IDE alternatives.

DiskOnChip IDE Pro is based on NAND flash technology. This technology is superior in its data storage characteristics, featuring the industry's highest write and erase performance, as well as the highest burst read/write transfer rate. Additionally, NAND flash technology is known for its high density and small die size, with the related cost and real estate benefits. Data integrity is guaranteed through embedded error detection and error correction code (EDC/ECC) that automatically detects and corrects data errors. The EDC/ECC algorithm is based on Hamming code and can detect up to 2 bits and correct 1 bit per 512 bytes.

DiskOnChip IDE Pro is ergonomically designed for easy installation and ready-to-run operation. Available in 40-pin and 44-pin connector packages, DiskOnChip IDE Pro fits easily into any platform with an IDE connector. A LED provides activity indication, while a specially designed case enables easy insertion. A screw hole can be used to secure DiskOnChip IDE Pro firmly in place.

| DiskOnChip | IDE Pro | is available in | capacities | ranging from | 16MB to | o 256MB, | making the | upgrade path | simple and |

|------------|---------|-----------------|------------|--------------|---------|----------|------------|--------------|------------|

| fast.      |         |                 |            |              |         |          |            |              |            |

|            |         |                 |            |              |         |          |            |              |            |

### 2.2 Pin Assignment

See Table 1 for the pin assignment of DiskOnChip IDE Pro.

Table 1: Pin Assignment

| Pin No.         | Signal | Function                         | Pin No.         | Sig    | nal              | Function               |

|-----------------|--------|----------------------------------|-----------------|--------|------------------|------------------------|

| 1               | RESET# | Host reset                       | 2               | GN     | ND               | Ground                 |

| 3               | HD7    | Host Data bit 7                  | 4               | Н      | D8               | Host Data bit 8        |

| 5               | HD6    | Host Data bit 6                  | 6               | Н      | <b>D</b> 9       | Host Data bit 9        |

| 7               | HD5    | Host Data bit 5                  | 8               | HD     | 10               | Host Data bit 10       |

| 9               | HD4    | Host Data bit 4                  | 10              | HC     | )11              | Host Data bit 11       |

| 11              | HD3    | Host Data bit 3                  | 12              | HC     | )12              | Host Data bit 12       |

| 13              | HD2    | Host Data bit 1                  | 14              | HC     | )13              | Host Data bit 13       |

| 15              | HD1    | Host Data bit 1                  | 16              | HC     | )14              | Host Data bit 14       |

| 17              | HD0    | Host Data bit 0                  | 18              | HC     | )15              | Host Data bit 15       |

| 19              | GND    | Ground                           | 20              | 40-pin | VCC <sup>1</sup> | Supply Voltage         |

|                 |        |                                  |                 | 44-pin | KEY              | Cut pin                |

| 21              | NC     | Not Connected                    | 22              | GN     | ND               | Ground                 |

| 23              | HIOW#  | Host I/O Write                   | 24              | GN     | ND               | Ground                 |

| 25              | HIOR#  | Host I/O Read                    | 26              | GN     | ND               | Ground                 |

| 27              | IORDY  | I/O Ready                        | 28              | CS     | EL               | Master/Slave<br>Select |

| 29              | NC     | Not Connected                    | 30              | GN     | ND               | Ground                 |

| 31              | INTRQ  | Interrupt Request                | 32              | IOIS   | 316#             | CS I/O 16-bit          |

| 33              | HA1    | Host Address bit 1               | 34              | PDI    | AG#              | Passed Diagnostics     |

| 35              | HA0    | Host Address bit 0               | 36              | H      | <b>A</b> 2       | Host Address bit 2     |

| 37              | CS0#   | Chip Select 0                    | 38              | CS1#   |                  | Chip Select 1          |

| 39              | DASP#  | Drive Active/<br>Drive 1 Present | 40              | GND    |                  | Ground                 |

| 41 <sup>2</sup> | VCC    | Supply Voltage                   | 42 <sup>2</sup> | VC     | CC               | Supply Voltage         |

| 43 <sup>2</sup> | GND    | Ground                           | 44 <sup>2</sup> | RESE   | RVED             | Reserved               |

|                 |        |                                  |                 |        |                  |                        |

<sup>1)</sup> In the 40-pin version, this pin is defined as VCC to reduce the need for an external power connector. In the 44-pin version, this pin is defined as KEY, according to the ATA standard.

NC = These pins are not connected internally.

RESERVED = All reserved signals must be left floating.

<sup>2)</sup> DiskOnChip IDE Pro 40-pin version does not contain pins 41-44.

# 2.3 Pin Description

Table 2 contains the pin description of DiskOnChip IDE Pro.

Table 2: Pin Description

| Signal                                                                                                                                                                                                                                                                                                                                       | Pin No.                                                                                                                                                           | Description                                                                                                                                                                                                                                                                                                                                                                                                       | Signal<br>Type |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|

| RESET#                                                                                                                                                                                                                                                                                                                                       | 1                                                                                                                                                                 | Host reset: Active low.                                                                                                                                                                                                                                                                                                                                                                                           | Input          |  |  |

| HD15-HD0  3-18  Host Data bus [15:0]. 16-bit bi-directional data input/output bus. HI the most significant bit, while HD0 is the least significant bit. This becarries data, commands and status information between the host a DiskOnChip IDE Pro. The lower 8 bits are used for 8-bit register transfers. Data transfers are 16-bits wide. |                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                   |                |  |  |

| DIOW#                                                                                                                                                                                                                                                                                                                                        | 23                                                                                                                                                                | Device I/O Write: Active low. Gates the data from the bus into DiskOnChip IDE Pro. The clocking occurs on the rising edge of the signal.                                                                                                                                                                                                                                                                          | Input          |  |  |

| DIOR#                                                                                                                                                                                                                                                                                                                                        | 25                                                                                                                                                                | Device I/O Read: Active low. Gates the data onto the bus from DiskOnChip IDE Pro. The clocking occurs on the falling edge of the signal.                                                                                                                                                                                                                                                                          | Input          |  |  |

| IORDY                                                                                                                                                                                                                                                                                                                                        | 27 I/O Ready: Negated by DiskOnChip IDE Pro to extend the host transfer cycle (Read or Write) when the device is not ready to respond to a data transfer request. |                                                                                                                                                                                                                                                                                                                                                                                                                   |                |  |  |

| CSEL                                                                                                                                                                                                                                                                                                                                         | 28                                                                                                                                                                | Configuration Select: Determines the device configuration as either Master or Slave. If CSEL is negated, then the device address is Master; if CSEL is asserted, then the device address is Slave.                                                                                                                                                                                                                |                |  |  |

| INTRQ                                                                                                                                                                                                                                                                                                                                        | 31                                                                                                                                                                | Interrupt Request: Interrupt request from DiskOnChip IDE Pro to the host. The output of this signal is tri-stated if the host disables the interrupt. When asserted, this signal is negated by the device within 400 nsec of the negation of DIOR# that reads the Status register. When asserted, this signal is negated by the device within 400 nsec of the negation of DIOW# that writes the Command register. | Output         |  |  |

| IOIS16#                                                                                                                                                                                                                                                                                                                                      | 32                                                                                                                                                                | I/O IS I6-Bit: Active low. Asserted (low) by DiskOnChip IDE Pro to indicate to the host that the current cycle is a 16-bit (word) data transfer. When the signal is negated (high), an 8-bit data transfer is performed.                                                                                                                                                                                          | Output         |  |  |

| HA2-HA0                                                                                                                                                                                                                                                                                                                                      | 33,35,36                                                                                                                                                          | Host Address bus HA[2:0]: Select the registers in the DiskOnChip IDE Pro controller.                                                                                                                                                                                                                                                                                                                              | Input          |  |  |

| PDIAG#                                                                                                                                                                                                                                                                                                                                       | 34                                                                                                                                                                | Passed Diagnostics: Active low. Informs the Master drive that the self-diagnostic of the Slave drive has ended.                                                                                                                                                                                                                                                                                                   | I/O            |  |  |

| CS0#                                                                                                                                                                                                                                                                                                                                         | 37                                                                                                                                                                | Host Chip Select 0: Active low. Selects the Command Block registers.                                                                                                                                                                                                                                                                                                                                              | Input          |  |  |

| CS1#                                                                                                                                                                                                                                                                                                                                         | 38                                                                                                                                                                | Host Chip Select 1: Active low. Selects the Command Block registers.                                                                                                                                                                                                                                                                                                                                              | Input          |  |  |

| DASP#                                                                                                                                                                                                                                                                                                                                        | 39                                                                                                                                                                | Drive Active/Drive1 Present: Active low. This is a time-multiplexed signal that indicates that a device is active, or that Device 1 is present.                                                                                                                                                                                                                                                                   | I/O            |  |  |

| GND                                                                                                                                                                                                                                                                                                                                          | 2,19,22,24,26,<br>30,40,43                                                                                                                                        | Ground                                                                                                                                                                                                                                                                                                                                                                                                            | Ground         |  |  |

| VCC                                                                                                                                                                                                                                                                                                                                          | 41, 42                                                                                                                                                            | Power supply                                                                                                                                                                                                                                                                                                                                                                                                      | Supply         |  |  |

# 2.4 Capacities and CHS (Cylinder, Head, Sector)

Table 3 shows the various capacities available for DiskOnChip IDE Pro, as well as the CHS (Cylinder, Head and Sector) for each capacity. If DiskOnChip IDE Pro is not identified or your platform does not support auto-detection, use the following parameters to complete the Drive Parameter Table.

Table 3: Drive Parameters

| Unformatted<br>Disk Capacity<br>(MB) | Formatted Disk<br>Capacity<br>(# of Sectors) | Cylinders | Heads | Sectors/Heads | Bytes/Sector |

|--------------------------------------|----------------------------------------------|-----------|-------|---------------|--------------|

| 16                                   | 31744                                        | 496       | 2     | 32            | 512          |

| 32                                   | 63488                                        | 992       | 2     | 32            | 512          |

| 64                                   | 126976                                       | 248       | 16    | 32            | 512          |

| 128                                  | 253952                                       | 496       | 16    | 32            | 512          |

| 256                                  | 507904                                       | 992       | 16    | 32            | 512          |

## 3. Theory of Operation

#### 3.1 Overview

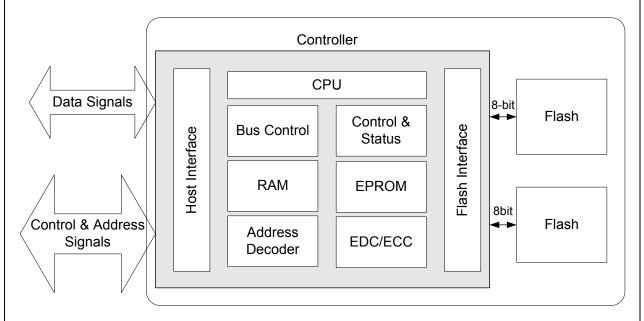

Figure 1 shows DiskOnChip IDE Pro operation from the system level, including the major hardware blocks.

Figure 1: DiskOnChip IDE Pro Block Diagram

DiskOnChip IDE Pro integrates an IDE controller and flash devices. Communication with the host occurs through the host interface, using the standard ATA protocol. Communication with the flash device(s) occurs through the flash interface.

The IDE controller incorporates a Control & Status block that consists of the Command Block registers. The ATA commands that instruct the IDE controller which operation needs to be executed are written/read from the Command Block registers. The data blocks are also transferred via the Command Block Registers. A description of the Command Block registers can be found in Section 4.

The embedded EDC/ECC mechanism is based on the Hamming code algorithm, and can detect up to 2 bits and correct 1 bit per 512 bytes.

## 4. Description of Command Block Registers

The Command Block registers are used for sending commands to the device or posting status from the device. These registers include the Cylinder High, Cylinder Low, Device/Head, Sector Count, Sector Number, Command, Status, Features, Error, and Data registers. The Control Block registers are used for device control and to post alternate status. These registers include the Device Control and Alternate Status registers.

#### 4.1 Status Register (Read)

This register contains the device status. The contents of this register are updated to reflect the current state of the device and the progress of any command being executed by the device. When BSY=0, the other bits in this register are valid. When BSY=1, other bits in this register are not valid. The contents of this register and all other Command Block Registers are not valid when the device is in Sleep mode.

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| BSY   | DRDY  | DF    | DSC   | DRQ   | CORR  | IDX   | ERR   |

| Bit No. | Description                                                                                                                                                                                               |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | ERR. When set, indicates that an error has occurred during the previous command execution. The bits in the Error register indicate the cause. See Section 5.2 for an overview of error codes.             |

| 1       | IDX (Index). Index is vendor specific.                                                                                                                                                                    |

| 2       | CORR (Corrected Data). Indicates a correctable data error. The definition of what constitutes a correctable error is vendor specific.                                                                     |

| 3       | DRQ (Data Request). When set, indicates that the device is ready to transfer a word or byte of data between the host and the device.                                                                      |

| 4       | DSC (Drive Seek Complete). When set, indicates that the requested sector was found.                                                                                                                       |

| 5       | DF (Device Fault). Indicates that a device fault error has been detected.                                                                                                                                 |

| 6       | DRDY (Device Ready). Indicates whether the device is capable of performing drive operations (commands). This bit is cleared at power up and remains cleared until the drive is ready to accept a command. |

| 7       | BSY (Busy). Set whenever the device has control of the Command Block registers. When BSY=1, the commands written to this register will be ignored by the device.                                          |

#### 4.2 Command Register (Write)

This register contains the ATA command code that the host sends to the device. Command execution begins immediately after this register is written. This register is write-only when BSY=0 and DRQ=0. The contents of this register and all other Command Block registers are not valid when the device is in Sleep mode.

| Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3   | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|--------|---------|-------|-------|-------|

|       |       |       | Commai | nd Code |       |       |       |

#### 4.3 Error Register (Read)

The Error register contains additional information about the source of an error. The content of this register is only valid when BSY=0 and DRQ=0 in the Status register and the ERR bit is asserted.

| Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|-------|-------|-------|-------|-------|-------|-------|

| Reserved | UNC   | MC    | IDNF  | MCR   | ABRT  | TKONF | AMNF  |

| Bit No. | Description                                                                                                                                                      |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | AMNF (Address Mark Not Found). Indicates that the data address mark has not been found after finding the correct ID field.                                       |

| 1       | TKONF (Track 0 Not Found). Indicates that track 0 has not been found during a RECALIBRATE command.                                                               |

| 2       | ABRT (Abort). Indicates that the requested command has been aborted because the command code or a command parameter is invalid or some other error has occurred. |

| 3       | MCR (Media Change Request). Not supported.                                                                                                                       |

| 4       | IDNF (ID-field Not Found). Requested sector ID-field Not Found.                                                                                                  |

| 5       | MC (Media Changed). Not supported.                                                                                                                               |

| 6       | UNC (Uncorrected). Non-correctable data error encountered.                                                                                                       |

| 7       | Reserved.                                                                                                                                                        |

#### 4.4 Feature Register (Write)

This register is command specific, and is write-only when BSY=0 and DRQ=0.

| Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3      | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|---------|------------|-------|-------|-------|

|       |       |       | Command | d Specific |       |       |       |

#### 4.5 Sector Number Register (LBA 0-7) (Read/Write)

The content of this register depends on the selected mode of address translation: CHS (Cylinder, Head, Sector) or LBA (Logical Block Address) mode. In CHS mode (LBA=0 in Device/Head register), this register contains the subsequent command's starting sector number, which can be from 1 to the maximum number of sectors per track. In LBA mode (LBA=1 in Device/Head register), this register contains LBA bits 0-7, which are updated upon command completion. This register is write-only when BSY=0 and DRQ=0.

| Bit 7    | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

|----------|----------|-------|-------|-------|-------|-------|-------|--|--|

| CHS Mode |          |       |       |       |       |       |       |  |  |

| SN7      | SN6      | SN5   | SN4   | SN3   | SN2   | SN1   | SN0   |  |  |

|          | LBA Mode |       |       |       |       |       |       |  |  |

| LBA7     | LBA6     | LBA5  | LBA5  | LBA3  | LBA2  | LBA1  | LBA0  |  |  |

| Bit No. | Description                  |  |  |  |  |  |  |  |

|---------|------------------------------|--|--|--|--|--|--|--|

|         | CHS Mode                     |  |  |  |  |  |  |  |

| 0-7     | SN[0:7] (Sector Numbers 0-7) |  |  |  |  |  |  |  |

|         | LBA Mode                     |  |  |  |  |  |  |  |

0-7 LBA[0:7] (Logical Block Addresses 0-7)

## 4.6 Cylinder Low Register (LBA 8-15) (Read/Write)

The contents of this register depend on the value of LBA bits 8-15 in the Device/Head register. If LBA=0, this register contains the 8 least significant bits of the starting cylinder address (CL bits 0-7). If LBA=1, this register contains LBA bits 8-15. This register is write-only when BSY=0 and DRQ=0.

| Bit 7    | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |  |  |

|----------|----------|-------|-------|-------|-------|-------|-------|--|--|--|--|--|

| CHS Mode |          |       |       |       |       |       |       |  |  |  |  |  |

| CL7      | CL6      | CL5   | CL4   | CL3   | CL2   | CL1   | CL0   |  |  |  |  |  |

|          | LBA Mode |       |       |       |       |       |       |  |  |  |  |  |

| LBA15    | LBA14    | LBA13 | LBA12 | LBA11 | LBA10 | LBA9  | LBA8  |  |  |  |  |  |

| Bit No. | Description                              |  |  |  |  |  |  |

|---------|------------------------------------------|--|--|--|--|--|--|

|         | CHS Mode                                 |  |  |  |  |  |  |

| 0-7     | CL[0:7] (Cylinder Low Bits 0-7)          |  |  |  |  |  |  |

|         | LBA Mode                                 |  |  |  |  |  |  |

| 0-7     | LBA[8:15] (Logical Block Addresses 8-15) |  |  |  |  |  |  |

## 4.7 Cylinder High Register (LBA 16-23) (Read/Write)

In CHS mode, the Cylinder High register contains the 8 high bits of the cylinder numbers, and reflects their status at command completion. In LBA mode, this register contains LBA bits 16-23 and reflects their status at command completion. This register is write-only when BSY=0 and DRQ=0.

| Bit 7    | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |  |

|----------|----------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| CHS Mode |          |       |       |       |       |       |       |  |  |  |  |

| CH7      | CH6      | CH5   | CH4   | CH3   | Ch2   | CH1   | CH0   |  |  |  |  |

|          | LBA Mode |       |       |       |       |       |       |  |  |  |  |

| LBA23    | LBA22    | LBA21 | LBA20 | LBA19 | LBA18 | LBA17 | LBA16 |  |  |  |  |

| Bit No. | Description                                |  |  |  |  |  |  |

|---------|--------------------------------------------|--|--|--|--|--|--|

|         | CHS Mode                                   |  |  |  |  |  |  |

| 0-7     | CH[0:7] (Cylinder High Bits 0-7)           |  |  |  |  |  |  |

|         | LBA Mode                                   |  |  |  |  |  |  |

| 0-7     | LBA[16:23] (Logical Block Addresses 16-23) |  |  |  |  |  |  |

## 4.8 Device/Head Register (Read/Write)

This register selects the device and defines address translation mode as CHS or LBA. In CHS mode it provides the head address. In LBA mode, it provides the assignment for LBA[27:24]. This register is write-only when BSY=0 and DRQ=0.

| Bit 7    | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |  |

|----------|----------|-------|-------|-------|-------|-------|-------|--|--|--|--|

| CHS Mode |          |       |       |       |       |       |       |  |  |  |  |

| 1        | LBA      | 1     | DEV   | HS3   | HS2   | HS1   | HS0   |  |  |  |  |

|          | LBA Mode |       |       |       |       |       |       |  |  |  |  |

|          | Rese     | rved  |       | LBA27 | LBA26 | LBA25 | LBA24 |  |  |  |  |

| Bit No. | Description                                                                                                                                                       |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | CHS Mode                                                                                                                                                          |

| 0-3     | HS[0:3] (Head Starting Address Bits 0-3). When LBA=0 (CHS), these bits contain the head address of the starting CHS address. Bit HS3 is the most significant bit. |

| 4       | DEV (Device Address). 0 = Master drive selected. 1 = Slave drive selected.                                                                                        |

| 6       | LBA (Address Mode Select).  0 = CHS (Cylinder, Head, Sector) mode.  1 = LBA (Logical Block Address) mode.                                                         |

|         | LBA Mode                                                                                                                                                          |

| 0-3     | LBA[24:27] (Logical Block Addresses 24-27). When LBA=1 (LBA mode), these bits represent LBA bits 24-27.                                                           |

| 4-7     | Reserved.                                                                                                                                                         |

#### 4.9 Sector Count Register (Read/Write)

The Sector Count register contains the number of data sectors requested to be transferred during a read or write operation between the host and the device. A zero value specifies 256 sectors. The command is successful if this register is zero on command completion. This register is write-only when BSY=0 and DRQ=0.

| Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|--------|-------|-------|-------|-------|

|       |       |       | Sector | Count |       |       |       |

#### 4.10 Data Register (Read/Write)

The Data register is a 16-bit register used to transfer data blocks between the device's data buffer and the host. This register can be written or the content is valid on read when DRQ=1.

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

| Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 |  |

|--------|--------|--------|--------|--------|--------|-------|-------|--|

| D15    | D14    | D13    | D12    | D11    | D10    | D9    | D8    |  |

#### 4.11 Alternate Status Register (Read)

This register contains the device status. The contents of this register are updated to reflect the current state of the device and the progress of any command being executed by the device. The contents of this register, except for BSY, is ignored when BSY=1. BSY is valid at all times. The contents of the register and all other Command Block registers are not valid while a device is in Sleep mode.

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| BSY   | DRDY  | DF    | DSC   | DRQ   | CORR  | IDX   | ERR   |

See Section 4.1 for the bit descriptions.

### 4.12 Device Control Register (Write)

This register allows a host to software reset attached devices and to enable or disable the assertion of the INTRQ signal by a selected device. This register can only be written when DMACK# is not asserted.

| Bit 7 | Bit 6 | Bit 5    | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0    |

|-------|-------|----------|-------|-------|-------|-------|----------|

|       |       | Reserved |       |       | SRST  | #IEN  | Reserved |

| Bit No. | Description                                                                                                                                           |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | Reserved. Clear this bit to 0.                                                                                                                        |

| 1       | #IEN (Interrupt Enable).  0 = Enables interrupts to the host (using the #IREQ tri-state pin).  1 = Disables all pending interrupts (#IREQ in high-Z). |

| 2       | SRST (Soft Reset). This is the host software reset bit.                                                                                               |

| 3-7     | Reserved.                                                                                                                                             |

# 5. Supported ATA Command Set

This section defines the format of the commands the host sends to DiskOnChip IDE Pro. The commands are issued to the device by loading the required registers in the command block with the supplied parameters, and then writing the command code to the register.

DiskOnChip IDE Pro supports the IDE commands listed in Table 4.

Table 4: Supported IDE Commands

| Command Code | Command Name                    |    |          | Register |    |     |

|--------------|---------------------------------|----|----------|----------|----|-----|

| Command Code | Command Name                    | FR | sc       | SN       | CY | D/H |

| 98h E5h      | CHECK POWER MODE                | -  | -        | -        | -  | D   |

| 90h          | EXECUTIVE DEVICE DIAGNOSTIC     | -  | -        | -        | -  | D   |

| ECh          | IDENTIFY DEVICE                 | -  | -        | -        | -  | D   |

| 97h E3h      | IDLE                            | -  | <b>✓</b> | -        | -  | D   |

| 95h E1h      | IDLE IMMEDIATE                  | -  | -        | -        | -  | D   |

| 91h          | INITIALIZE DEVICE<br>PARAMETERS | -  | <b>√</b> | -        | -  | D+H |

| E4h          | READ BUFFER                     | -  | -        | -        | -  | D   |

| C4h          | READ MULTIPLE                   | -  | ✓        | ✓        | ✓  | D+H |

| 20h 21h      | READ SECTOR(S)                  | -  | <b>✓</b> | ✓        | ✓  | D+H |

| 22h 23h      | READ LONG SECTOR(S)             | -  | -        | ✓        | ✓  | D+H |

| 40h 41h      | READ VERIFY<br>SECTOR(S)        | -  | <b>√</b> | <b>√</b> | ✓  | D+H |

| 10h          | RECALIBRATE                     | -  | -        | -        | -  | D   |

| 70h          | SEEK                            | =  | -        | ✓        | ✓  | D+H |

| EFh          | SET FEATURES                    | ✓  | -        | -        | -  | D   |

| C6h          | SET MULTIPLE MODE               | -  | <b>✓</b> | -        | -  | D   |

| 99h E6h      | SET SLEEP MODE                  | -  | -        | -        | -  | D   |

| 96h E2h      | STANDBY                         | =  | -        | -        | -  | D   |

| 94h E0h      | STANDBY IMMEDIATE               | -  | -        | -        | -  | D   |

| E8h          | WRITE BUFFER                    | -  | -        | -        | -  | D   |

| 3Ch          | WRITE VERIFY                    | -  | <b>✓</b> | ✓        | ✓  | ✓   |

| C5h          | WRITE MULTIPLE                  | -  | ✓        | ✓        | ✓  | D+H |

| 30h 31h      | WRITE SECTOR(S)                 | -  | ✓        | ✓        | ✓  | D+H |

| 32h 33h      | WRITE LONG SECTOR(S)            | -  | ✓        | ✓        | ✓  | D+H |

| 00h          | NOP                             | -  | -        | -        | -  | D   |

Definition of Abbreviations:

Registers – FR: Feature register, SC: Sector Count register, SN: Sector Number register, CY: Cylinder registers, DH: Drive/Head register

Symbols – ✓: The register is valid, D: Only drive parameters are valid, H: Only head parameters are valid

## 5.1 Command Set Description

#### 5.1.1 Check Power Mode – 98h, E5h

This command checks the current power mode of DiskOnChip IDE Pro.

When this command is issued in Sleep mode, or is being set to/recovering from Sleep mode, DiskOnChip IDE Pro sets the BSY bit in the Status register and the Sector Count register to 00h. Then the BSY bit is cleared, and an interrupt is generated.

When DiskOnChip IDE Pro is in Idle mode, it sets the BSY bit in the Status register and the Sector Count register to FFh. Then the BSY bit in the Status register is cleared, and an interrupt is generated.

| INPUT         |   |            |   |   |   |   |   |   |  |  |

|---------------|---|------------|---|---|---|---|---|---|--|--|

| Register      | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

| Features      |   |            |   |   |   |   |   |   |  |  |

| Sector Count  |   |            |   |   |   |   |   |   |  |  |

| Sector Number |   |            |   |   |   |   |   |   |  |  |

| Cylinder Low  |   |            |   |   |   |   |   |   |  |  |

| Cylinder High |   |            |   |   |   |   |   |   |  |  |

| Device/Head   | 1 |            | 1 | D |   |   |   |   |  |  |

| Command       |   | 98h or E5h |   |   |   |   |   |   |  |  |

| OUTPUT       |     |      |      |            |            |      |       |      |  |

|--------------|-----|------|------|------------|------------|------|-------|------|--|

| Register     | 7   | 6    | 5    | 4          | 3          | 2    | 1     | 0    |  |

| Status       | BSY | DRDY | DF   | DSC        | DRQ        | CORR | IDX   | ERR  |  |

|              | 0   | 1    | 0    | 1          | 0          | 0    | 0     | 0    |  |

| Sector Count |     |      | Powe | er Mode Co | de (00h oi | FFh) |       |      |  |

| Error        | R   | UNC  | MC   | IDNF       | MCR        | ABRT | TKONF | AMNF |  |

|              |     | 0    | 0    | 0          | 0          | 0    | 0     | 0    |  |

### 5.1.2 Execute Drive Diagnostics - 90h

This command performs self-diagnostics on various internal components of DiskOnChip IDE Pro. Results of the diagnostics are reported in the Error register. Note that the bit definitions for the Error register do not apply to this command. Instead, the value in the Error register is a diagnostic code.

| INPUT         |   |   |   |    |    |   |   |   |  |  |  |

|---------------|---|---|---|----|----|---|---|---|--|--|--|

| Register      | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

| Features      |   |   |   |    |    |   |   |   |  |  |  |

| Sector Count  |   |   |   |    |    |   |   |   |  |  |  |

| Sector Number |   |   |   |    |    |   |   |   |  |  |  |

| Cylinder Low  |   |   |   |    |    |   |   |   |  |  |  |

| Cylinder High |   |   |   |    |    |   |   |   |  |  |  |

| Device/Head   |   |   |   | D  |    |   |   |   |  |  |  |

| Command       |   |   |   | 90 | )h | • |   |   |  |  |  |

| OUTPUT   |     |                             |    |     |     |      |     |     |  |  |

|----------|-----|-----------------------------|----|-----|-----|------|-----|-----|--|--|

| Register | 7   | 6                           | 5  | 4   | 3   | 2    | 1   | 0   |  |  |

| Status   | BSY | DRDY                        | DF | DSC | DRQ | CORR | IDX | ERR |  |  |

|          | 0   | ✓                           | 0  | ✓   | ✓   | ✓    | 0   | ✓   |  |  |

| Error    |     | Diagnostic code (see below) |    |     |     |      |     |     |  |  |

| Code | Description            |  |  |  |  |  |  |  |

|------|------------------------|--|--|--|--|--|--|--|

| 01H  | No error detected      |  |  |  |  |  |  |  |

| 02H  | Formatter device error |  |  |  |  |  |  |  |

| 03H  | Sector buffer error    |  |  |  |  |  |  |  |

| 04H  | ECC logic error        |  |  |  |  |  |  |  |

| 05H  | Slave failed           |  |  |  |  |  |  |  |

### 5.1.3 Identify Drive – ECh

The Identify Drive command enables the host to receive parameter information from DiskOnChip IDE Pro. When the command is issued, the device performs the following sequence: sets the BSY bit, prepares to transfer the 256 words of device identification data to the host, sets the DRQ bit, clears the BSY bit, and generates an interrupt. The host can then transfer the data by reading the Data register. All reserved bits or words are set to 0. See Table 5 to identify drive information for this device.

| INPUT         |   |   |   |   |    |   |   |   |  |  |

|---------------|---|---|---|---|----|---|---|---|--|--|

| Register      | 7 | 6 | 5 | 4 | 3  | 2 | 1 | 0 |  |  |

| Features      |   |   |   |   |    |   |   |   |  |  |

| Sector Count  |   |   |   |   |    |   |   |   |  |  |

| Sector Number |   |   |   |   |    |   |   |   |  |  |

| Cylinder Low  |   |   |   |   |    |   |   |   |  |  |

| Cylinder High |   |   |   |   |    |   |   |   |  |  |

| Device/Head   |   |   |   | D |    |   |   |   |  |  |

| Command       |   |   |   | E | Ch |   |   |   |  |  |

| OUTPUT   |     |      |    |      |     |      |       |      |  |  |

|----------|-----|------|----|------|-----|------|-------|------|--|--|

| Register | 7   | 6    | 5  | 4    | 3   | 2    | 1     | 0    |  |  |

| Status   | BSY | DRDY | DF | DSC  | DRQ | CORR | IDX   | ERR  |  |  |

|          | 0   | ✓    | 0  | 1    | ✓   | ✓    | 0     | 0    |  |  |

| Error    | R   | UNC  | MC | IDNF | MCR | ABRT | TKONF | AMNF |  |  |

|          |     | 0    | 0  | 0    | 0   | ✓    | 0     | 0    |  |  |

Table 5: Identify Drive Descriptions

| Word    | Data  | Description                                                    |

|---------|-------|----------------------------------------------------------------|

| 0       | 040AH | General configuration bit-significant information              |

| 1       | XXXX  | Number of cylinders                                            |

| 2       | 0000H | Reserved                                                       |

| 3       | XXXX  | Number of heads                                                |

| 4       | 0000H | Number of unformatted bytes per track                          |

| 5       | 0200H | Number of unformatted bytes per sector                         |

| 6       | XXXX  | Number of sectors per track                                    |

| 7-8     | XXXX  | Number of sectors per device (Word7= MSW, Word 8= LSW)         |

| 9       | 0000H | Reserved                                                       |

| 10-19   | XXXX  | Serial Number in ASCII                                         |

| 20      | 0002H | Buffer type: dual ported, multi-sector, with read cache        |

| 21      | 0002H | Buffer size in 512 byte increments                             |

| 22      | 0004H | # of ECC bytes passed on Read/Write Long Commands              |

| 23-26   | XXXX  | Firmware revision in ASCII                                     |

| 27-46   | XXXX  | Model number in ASCII                                          |

| 47      | 0001H | Maximum of 1 sector on Read/Write Multiple command             |

| 48      | 0000H | Cannot perform double word I/O (32 bits)                       |

| 49      | 0200H | Capabilities: DMA not Supported (bit 8), LBA supported (bit 9) |

| 50      | 0000H | Reserved                                                       |

| 51      | 0200H | PIO data transfer cycle timing mode 2                          |

| 52      | 0000H | DMA data transfer cycle timing mode not supported              |

| 53      | 0001H | Word 54-58 are valid                                           |

| 54      | XXXX  | Current numbers of cylinders                                   |

| 55      | XXXX  | Current numbers of heads                                       |

| 56      | XXXX  | Current sectors per track                                      |

| 57-58   | XXXX  | Current capacity in sectors (LBA)(Word 57= LSW, Word 58= MSW)  |

| 59      | 010XH | Multiple sector setting is valid                               |

| 60-61   | XXXX  | Total number of sectors addressable in LBA Mode                |

| 62-127  | 0000H | Reserved                                                       |

| 128-159 | 0000H | Reserved vendor unique bytes                                   |

| 160-255 | 0000H | Reserved                                                       |

### 5.1.4 Idle - 97h, E3h

This command causes DiskOnChip IDE Pro to set BSY, enter Idle mode, clear BSY and generate an interrupt. If the sector count is not 0, it is intercepted as a timer count (with a time base of 5 milliseconds, which differs from the ATA specification) and automatic Power-Down mode is enabled. If the sector count is 0, automatic Power-Down mode is disabled.

| INPUT         |   |                                 |   |       |        |   |   |   |  |  |  |  |

|---------------|---|---------------------------------|---|-------|--------|---|---|---|--|--|--|--|

| Register      | 7 | 6                               | 5 | 4     | 3      | 2 | 1 | 0 |  |  |  |  |

| Features      |   |                                 |   |       |        |   |   |   |  |  |  |  |

| Sector Count  |   | Timer Count (5 msec increments) |   |       |        |   |   |   |  |  |  |  |

| Sector Number |   |                                 |   |       |        |   |   |   |  |  |  |  |

| Cylinder Low  |   |                                 |   |       |        |   |   |   |  |  |  |  |

| Cylinder High |   |                                 |   |       |        |   |   |   |  |  |  |  |

| Device/Head   |   |                                 |   | D     |        |   |   |   |  |  |  |  |

| Command       |   |                                 |   | E3h c | or 97h |   |   |   |  |  |  |  |

| OUTPUT   |     |      |    |      |     |      |       |      |  |  |

|----------|-----|------|----|------|-----|------|-------|------|--|--|

| Register | 7   | 6    | 5  | 4    | 3   | 2    | 1     | 0    |  |  |

| Status   | BSY | DRDY | DF | DSC  | DRQ | CORR | IDX   | ERR  |  |  |

|          | 0   | ✓    | 0  | 1    | 0   | 0    | 0     | ✓    |  |  |

| Error    | R   | UNC  | MC | IDNF | MCR | ABRT | TKONF | AMNF |  |  |

|          |     | 0    | 0  | 0    | 0   | ✓    | 0     | 0    |  |  |

### 5.1.5 Idle Immediate – 95h, E1h

This command causes DiskOnChip IDE Pro to set BSY, enter Idle mode, clear BSY and generate an interrupt.

| INPUT         |   |   |   |       |        |   |   |   |  |

|---------------|---|---|---|-------|--------|---|---|---|--|

| Register      | 7 | 6 | 5 | 4     | 3      | 2 | 1 | 0 |  |

| Features      |   |   |   |       |        |   |   |   |  |

| Sector Count  |   |   |   |       |        |   |   |   |  |

| Sector Number |   |   |   |       |        |   |   |   |  |

| Cylinder Low  |   |   |   |       |        |   |   |   |  |

| Cylinder High |   |   |   |       |        |   |   |   |  |

| Device/Head   |   |   |   | D     |        |   |   |   |  |

| Command       |   |   |   | E1h c | or 95h |   |   |   |  |

| OUTPUT   |     |      |    |     |     |      |     |     |  |

|----------|-----|------|----|-----|-----|------|-----|-----|--|

| Register | 7   | 6    | 5  | 4   | 3   | 2    | 1   | 0   |  |

| Status   | BSY | DRDY | DF | DSC | DRQ | CORR | IDX | ERR |  |

|          | 0   | ✓    | 0  | 1   | 0   | 0    | 0   | ✓   |  |

| Error | R | UNC | MC | IDNF | MCR | ABRT | TKONF | AMNF |

|-------|---|-----|----|------|-----|------|-------|------|

|       |   | 0   | 0  | 0    | 0   | ✓    | 0     | 0    |

#### 5.1.6 Initialize Drive Parameters – 91h

Initialize Drive Parameters allows the host to alter the number of sectors per track and the number of heads per cylinder. This command does not check the validity of counts of sectors and heads. If an invalid value is set, an error is reported when another command attempts an invalid access. The Sector Count register specifies the number of logical sectors per logical track, and the Device/Head register specifies the maximum head number.

| INPUT         |   |   |     |             |              |            |            |    |  |  |  |

|---------------|---|---|-----|-------------|--------------|------------|------------|----|--|--|--|

| Register      | 7 | 6 | 5   | 4           | 3            | 2          | 1          | 0  |  |  |  |

| Features      |   |   |     |             |              |            |            |    |  |  |  |

| Sector Count  |   |   | Nur | nber of sec | ctors per tr | ack.       |            |    |  |  |  |

| Sector Number |   |   |     |             |              |            |            |    |  |  |  |

| Cylinder Low  |   |   |     |             |              |            |            |    |  |  |  |

| Cylinder High |   |   |     |             |              |            |            |    |  |  |  |

| Device/Head   | Х | 0 | Х   | D           | Н            | ead counts | per cylind | er |  |  |  |

| Command       |   |   |     | 9′          | 1h           |            |            |    |  |  |  |

|          | OUTPUT |      |    |      |     |          |       |      |  |

|----------|--------|------|----|------|-----|----------|-------|------|--|

| Register | 7      | 6    | 5  | 4    | 3   | 2        | 1     | 0    |  |

| Status   | BSY    | DRDY | DF | DSC  | DRQ | CORR     | IDX   | ERR  |  |

|          | 0      | ✓    | 0  | 1    | ✓   | ✓        | 0     | ✓    |  |

| Error    | R      | UNC  | MC | IDNF | MCR | ABRT     | TKONF | AMNF |  |

|          |        | 0    | 0  | 0    | 0   | <b>√</b> | 0     | 0    |  |

#### 5.1.7 Read Buffer - E4h

This command enables the host to read the current contents of the device's sector buffer. When this command is issued, the device sets the BSY bit, enables the sector buffer for a read operation, sets the DRQ bit, clears the BSY bit, and generates an interrupt. The host then reads the data from the buffer.

| INPUT         |   |   |   |    |    |   |   |   |  |

|---------------|---|---|---|----|----|---|---|---|--|

| Register      | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 |  |

| Features      |   |   |   |    |    |   |   |   |  |

| Sector Count  |   |   |   |    |    |   |   |   |  |

| Sector Number |   |   |   |    |    |   |   |   |  |

| Cylinder Low  |   |   |   |    |    |   |   |   |  |

| Cylinder High |   |   |   |    |    |   |   |   |  |

| Device/Head   |   |   |   | D  |    |   |   |   |  |

| Command       |   |   |   | E4 | 4h |   |   |   |  |

|          |   |   | OU. | TPUT |   |   |   |   |

|----------|---|---|-----|------|---|---|---|---|

| Register | 7 | 6 | 5   | 4    | 3 | 2 | 1 | 0 |

| Status | BSY | DRDY | DF | DSC  | DRQ | CORR | IDX   | ERR  |

|--------|-----|------|----|------|-----|------|-------|------|

|        | 0   | ✓    | 0  | 1    | 1   | 0    | 0     | ✓    |

| Error  | R   | UNC  | MC | IDNF | MCR | ABRT | TKONF | AMNF |

|        |     | 0    | 0  | 0    | 0   | ✓    | 0     | 0    |

#### 5.1.8 Read Multiple - C4h

This command functions like the Read Sector(s) command, but instead of issuing interrupts for each sector, it issues interrupts when a block is transferred that contains the counts of sectors defined by the Set Multiple command. The DRQ required for the transfer should be set only at the start of the data block and does not affect other sectors. When the Read Multiple command is issued, the requested sectors (not the block counts or the sector counts in a block) are written into the Sector Count register. Errors occurring during command execution are reported at the start of a complete or partial block transfer. The transfer continues even if DRQ is set and the data is corrupted. After the data transfer, the task file content (with the block data containing the sectors where the error occurred) is undefined. To obtain valid error information the host must request a re-transmission. The next block or part of a block is transferred only if the error is correctable. For all other errors, the command is aborted after transferring a block containing an error.

| INPUT         |   |         |               |              |              |             |           |   |  |  |  |

|---------------|---|---------|---------------|--------------|--------------|-------------|-----------|---|--|--|--|

| Register      | 7 | 6       | 5             | 4            | 3            | 2           | 1         | 0 |  |  |  |

| Features      |   |         |               |              |              |             |           |   |  |  |  |

| Sector Count  |   | Th      | e number      | of sectors/l | ogical bloc  | ks to trans | fer       |   |  |  |  |

| Sector Number |   | Sect    | or[7:0] or L  | BA[7:0] of   | the sector   | LBA to tra  | nsfer     |   |  |  |  |

| Cylinder Low  |   | Cylind  | ler[7:0] or L | _BA[15:8] c  | of the secto | r/LBA to tr | ansfer    |   |  |  |  |

| Cylinder High |   | Cylinde | r[15:8] or L  | BA[23:16]    | of the sec   | tor/LBA to  | transfer  |   |  |  |  |

| Device/Head   | 1 | LBA     | 1             | D            |              | Head (LE    | 3A 27-24) |   |  |  |  |

| Command       |   |         |               | C.           | 4h           |             |           |   |  |  |  |

|               | OUTPUT |          |    |      |     |      |       |      |  |  |  |

|---------------|--------|----------|----|------|-----|------|-------|------|--|--|--|

| Register      | 7      | 6        | 5  | 4    | 3   | 2    | 1     | 0    |  |  |  |

| Status        | BSY    | DRDY     | DF | DSC  | DRQ | CORR | IDX   | ERR  |  |  |  |

|               | 0      | ✓        | 0  | 1    | ✓   | ✓    | 0     | ✓    |  |  |  |

| Sector Count  |        |          |    |      |     |      |       |      |  |  |  |

| Sector Number |        |          |    |      |     |      |       |      |  |  |  |

| Cylinder Low  |        |          |    |      |     |      |       |      |  |  |  |

| Cylinder High |        |          |    |      |     |      |       |      |  |  |  |

| Device/Head   |        |          |    |      |     |      |       |      |  |  |  |

|               |        |          |    |      |     |      |       |      |  |  |  |

|               |        |          |    |      |     |      |       |      |  |  |  |

|               |        |          |    |      |     |      |       |      |  |  |  |

| Error         | R      | UNC      | MC | IDNF | MCR | ABRT | TKONF | AMNF |  |  |  |

|               |        | <b>√</b> | 0  | ✓    | 0   | ✓    | 0     | 0    |  |  |  |

| 5.1.9 Read Sector(s) – 20h, 21h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| This command allows the host to read up to 256 sectors as specified in the Sector Count register. A sector count of 0 indicates a transfer request of 256 sectors. The transfer starts from the sector specified in the Sector Number register. DRQ is set prior to the transfer, regardless of the error state. The command ends by placing the cylinder, head and sector number of the last read sector in the task file. If an error occurs, the read operation aborts in the sector with the error. The Cylinder, Head and Sector number of the sector with the error is placed in the task file. The error data remains in the data buffer. The Cylinder Low, Cylinder High, Device/Head and Sector Number or LBA registers |

| specify the starting sector address to be read. The Sector Count register specifies the number of sectors to be transferred.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |